(ii) VHDL descr iption Write the VHDL description of a 4-bit wide 4x1 multiplexer designed using 4x1 Mux.

Dynamic characteristics of a 4x1 Pass Transistor MUX using NgSpice. The even-numbered AND gates, on the other hand, follow the logic state of A. Design of 2 Bit Comparator Using When-Else Stateme. for mux 2 input 0 is the input for first arm of mux2 and in the second arm of multiplexer 2 is data A while B as select line, both the data processed by multiplexer and gives the output Q i.

Parallel input serial output shift register verilog code code#

Counter 2-bit: The VHDL source code can be found here: Count2bit_VHDL. T here are two data inputs D0 and D1, and a select input called S. Since, each 4×1 Multiplexer produces one output, we require a 2×1 Multiplexer in second stage by considering the outputs of first stage as inputs and to produce the final output. Actually my requirement in a design is to use 4 bit. Each one of the remaining AND gates is connected in a binary pattern to either the direct or the inverted control inputs of. In this post we are sharing with you the verilog code of different multiplexers such as 2:1 MUX, 4:1 MUX etc. I am sure you are aware of with working of a Multiplexer. It also takes into consideration borrow of the lower significant stage. (ii) SImulation# Simulate the 4-bit 4x1 multiplexer using the generic testbench to confirm the correctness of your description. 8 V differential: SHF C911 A: 4-Bit DAC: 5… 67 Gbps at 2, 3 or 4 inputs: 5… 67 GBaud 4, 8 or 16 levels: 0. T A I M xy D I0 I1 I2 I3 D From the car’s s1s0 To the above-central computer mirror display 4x1 8-bit button We’ll design this later 8 8 8 8 8 28 Using 2-to-1 multiplexers to build a 4-to-1 multiplexer.

This is the second input line of the 2:1 Multiplexer. Audio Q: = 2 mA and VCEQ 10 V, determine R, and Re for the %3D t Given that Ico network of Fig. 6-Bit DAC: 1… 60 Gbps at 2 to 6 inputs: 1… 60 GBaud 4 to 64 levels: 1. Our vast portfolio of I 2 C logic products includes a selection of multiplexers and switches for connecting an upstream I 2 C-bus to any combination of downstream I 2 C buses. Re: digital question Hi friends, I got a solution for the question, To built 4 - bit 2's complement number using minimum number of 2:1 Mux.Reversible 4x1 Multiplexer Using RMUX1 Gates. So lets explore the NAND gate a little bit. The multiplexer will select either a, b, c, or d based on the select signal sel using the assign statement. Small Description about Structural Modeling Style.

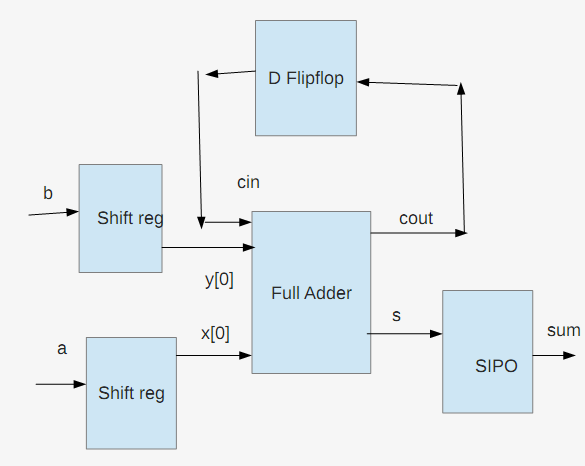

Implement an 8x1 multiplexer using VHDL structural modeling. to' inputs of the decoder is the selection lines of 4X1 MUX outputs of decoder is given to with multiplexer output of the or gate output of gates along AND inputs is ou 4X1 MUX X 4 bit register using D-Flip flop Registers operate in one of 4 different modes Those are li serial in Serial out Register 2 serial in Parallel out register 3- parallel in- serial out register 4 Parallel in In.

0 kommentar(er)

0 kommentar(er)